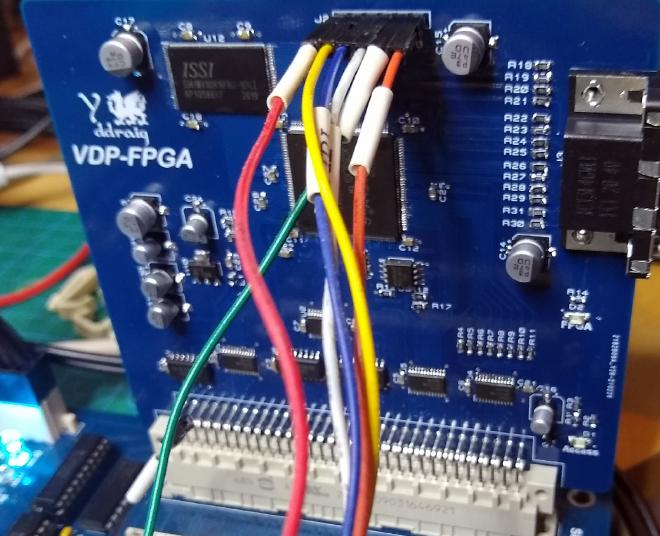

FPGA Video card testing

The FPGA video card has been built up. A couple of mistakes in ordering the parts so I ended up with a couple of capacitors that have the wrong footprint but were still usable. Unfortunately I ordered the wrong version of the 1.2V regulator and couldn’t use and had no substitute for. Waiting for the correct part set me back a few days, but once that was on the board and a few basic tests were done to make sure all voltage levels were correct it was time to start testing.

I had some VGA display code previously written for a Mimas V2 FPGA dev board so I didn’t need to start completely from scratch.

I was able to get VGA output running reasonably quickly which was a fantastic milestone since this was the first FPGA based board I had designed. While getting a working VGA port is an excellent start, it is only one small part of the overall board so there is still a lot of work to do before I canfully claim it as a success.

On the Mimas dev board, my test code cycled through four VGA test patterns using an onboard button. My goal was to reproduce the same behavior, but controlled by the 68000 instead.

To do this, I wrote some code to simply read the data bus when the select line to the video card is asserted and use the lower 2 bits to set the video mode. This would prove that the basics of the bus interface were working correctly. There were a few false starts on getting this running, mainly due to me forgetting to enable the data bus buffers to the FPGA but once they were fixed, I was able to control the video mode from the monitor program on the board.

The next goal is to have the 68000 write an image to SRAM and then have the FPGA read that data to generate VGA output. I’ve already made some progress with SRAM reads and have initial results working, but there’s more to do before I can display meaningful graphics.

One unresolved issue that I still have to address is the Flash memory on the board. The part I’m using isn’t recognised by the version of ISE WebPACK that I’m using, and many of the supported parts are long out of production. I have to program the FPGA via JTAG every time I power up the board—not ideal. I’ll either need to find a workaround for this device or source a compatible replacement.

Next update will hopefully have something a bit more interesting to show.